Intro

기본적인 MIPS CPU의 구조의 구체적인 사항을 점점 완성시키며 MIPS CPU의 구성 요소를 살펴볼 것이다.

이 문서는 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface 책에서 대부분의 내용을 가져왔다.

Basic MIPS architecture

여러 가지 MIPS 명령어에 따라 세부적인 CPU가 해야 할 동작은 다르지만, 기본적으로 수행해야 할 동작은 다음과 같다.

모든 명령어에서 첫 두 단계는 동일하다.

- 프로그램 카운터(PC)를 명령어가 포함된 메모리에 보내고, 해당 메모리에서 명령어를 가져온다.

- 명령어 필드를 사용하여 읽을 레지스터를 선택하고, 한 개 또는 두 개의 레지스터를 읽는다.

lw명령어의 경우 한 개의 레지스터만 읽으면 되지만, 대부분의 다른 명령어는 두 개의 레지스터를 읽어야 한다.

이 두 단계를 수행한 후에는 명령어 클래스에 따라 완료해야 할 작업이 달라진다. 다행히도, 세 가지 명령어 클래스(메모리 참조, 산술-논리 연산, 분기)의 경우 정확한 명령어와 관계없이 필요한 작업이 대부분 동일하다.

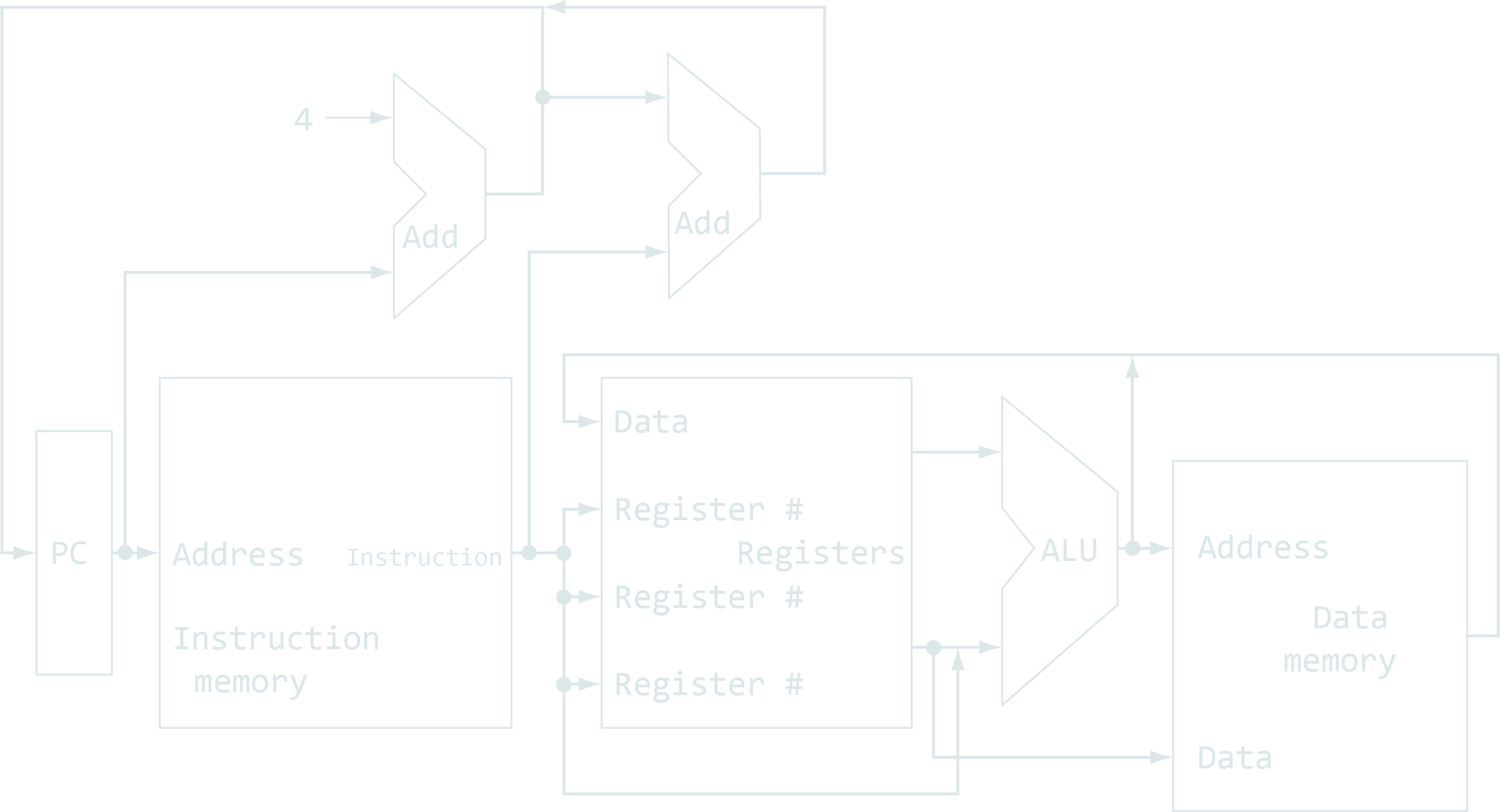

이에 맞추어 개략적인 CPU의 구조를 그리면 다음과 같을 것이다.

기본적인 PC (program counter), Instruction Memory, Register, 데이터 메모리, Adder가 보인다. 하지만 이 구성으로는 부족하다.

What’s more?

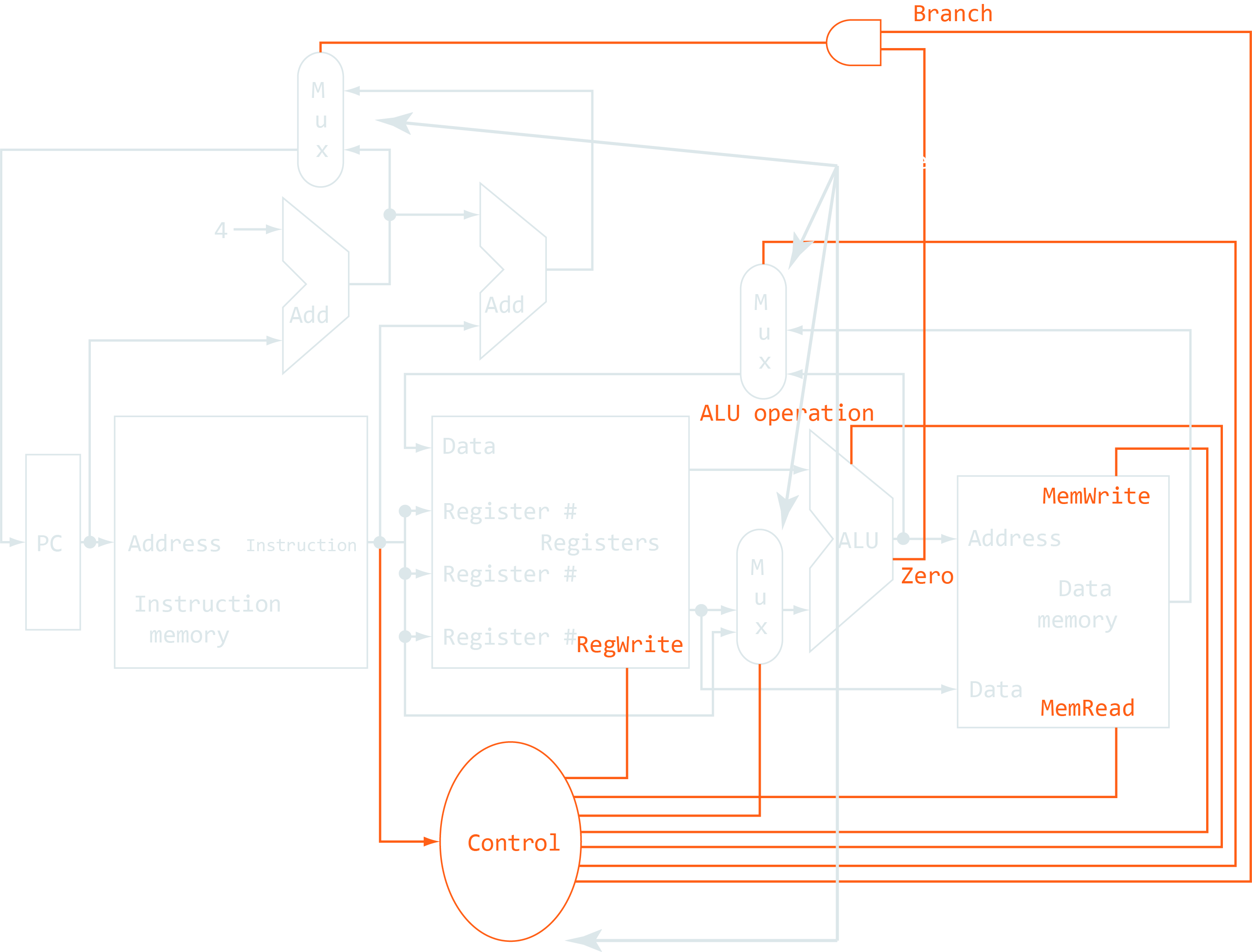

위 그림에서 어떤 것이 더 추가되어야 할까?

Multiplexor: 특정 유닛으로 전달되는 데이터가 두 가지 다른 소스에서 오는 경우가 있다. PC에 쓰이는 값은 두 개의 Adder 중 하나에서 올 수 있다 : 레지스터 파일에 쓰이는 데이터는 ALU 또는 데이터 메모리 이 데이터 라인들을 단순히 연결할 수는 없으며, 여러 소스 중에서 하나를 선택하여 목적지로 전달하는 논리 소자가 필요하다. 이러한 선택은 일반적으로 멀티플렉서(multiplexor) 라고 불리는 장치를 통해 이루어져야 한다.

Control Unit: 위 그림에서, 몇몇 유닛은 명령어 유형에 따라 제어되어야 한다. 예를 들어, 데이터 메모리는

load시 읽어야 하고,store시에는 써야 한다. 레지스터 파일은load나 산술-논리 명령어에서만 쓰여야 한다. 그리고 이에 맞추어, ALU는 다양한 작업을 수행할 수 있어야 한다. 멀티플렉서와 마찬가지로 제어 라인 (Control line)은 명령어의 다양한 필드를 기반으로 설정되어 이들 작업을 수행하도록 지시한다.

Basics of Logic Design

MIPS CPU의 내부 요소를 살펴보기 전에, 아주 기본적으로 컴퓨터의 논리 회로가 어떻게 동작하는지를 간단히 살펴보아야 한다.

Combinational & State

MIPS의 Datapath들은 두 가지 다른 유형의 논리 요소로 구성된다. 데이터 값을 처리하는 요소와 상태를 포함하는 요소이다.

- 데이터 값을 처리하는 요소들은 모두 조합 요소(combinational element)로, 이는 출력이 현재 입력에만 의존함을 의미한다. 동일한 입력이 주어지면 조합 요소는 항상 동일한 출력을 생성한다.

- 설계의 다른 요소들은 조합 논리가 아닌 상태를 포함한다. 상태를 포함하는 요소는 내부 저장 공간을 가지고 있다. 이러한 요소들을 상태 요소(state element)라고 부르는데, (혹은 Sequential element) 컴퓨터의 전원을 끊은 후 다시 시작할 때, 전원을 끄기 전의 값을 상태 요소에 로드하면 정확하게 재시작할 수 있기 때문이다.

앞으로 Combinational element를 간단히 Combi, State element (Sequential element)를 State로 부를 것이다.

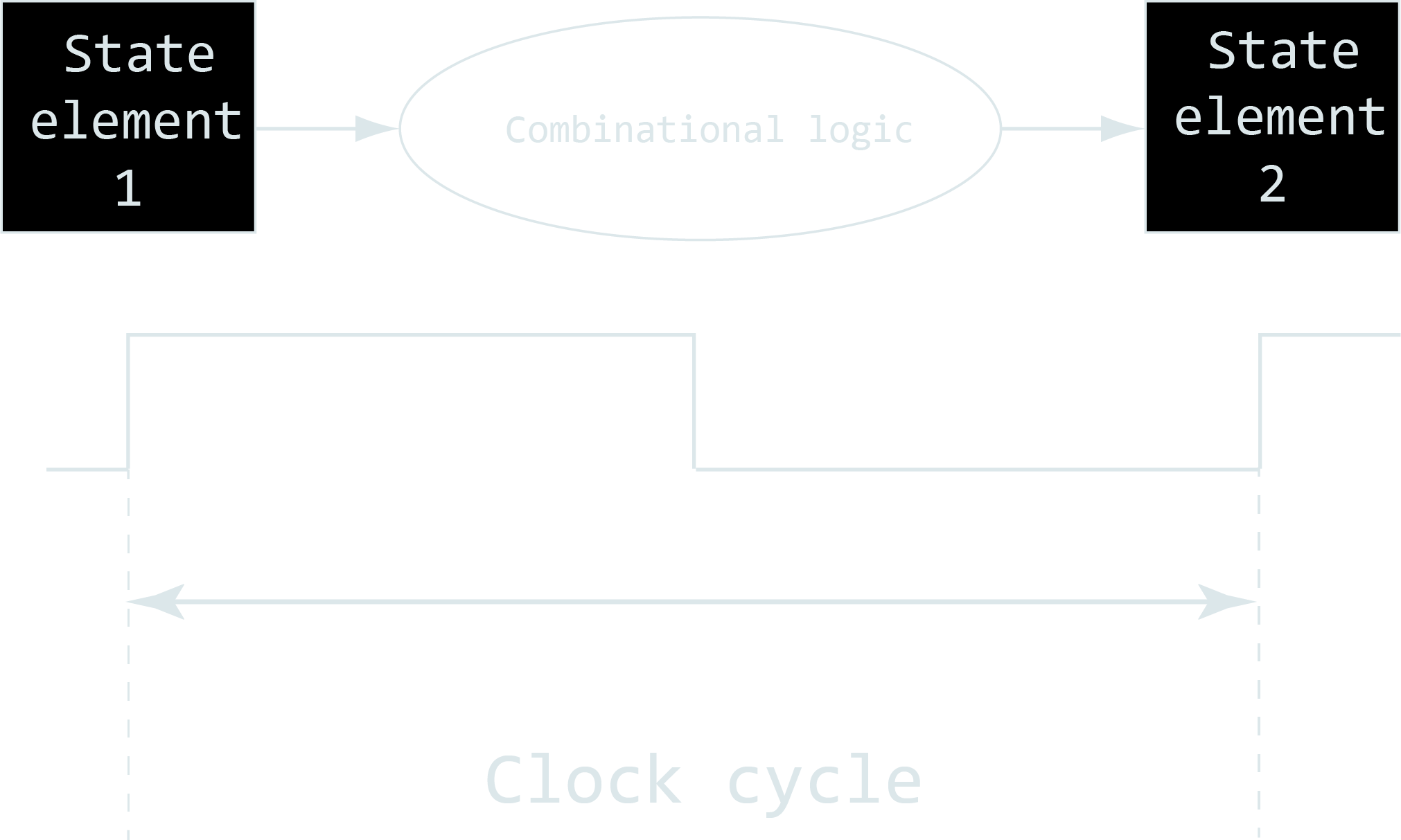

Clocking methodology

Clocking methodology는 신호가 언제 읽히고 언제 기록될 수 있는지를 정의한다. 읽기와 쓰기의 타이밍을 명확히 규정하는 것이 중요한 이유는 신호가 읽히는 동시에 기록될 때, 읽기 값이 이전 값, 새로 기록된 값, 혹은 이 둘의 혼합일 수 있기 때문이다. 컴퓨터 설계는 이러한 불확실성을 허용할 수 없다. 클럭 방법론은 하드웨어의 예측 가능성을 보장하기 위해 설계된다.

여기서는 간단함을 위해 엣지 트리거(edge-triggered) Clocking methodology을 가정한다. 이것은 상태 요소에 저장된 값이 클럭 엣지, 즉 짧은 시간 내에 발생하는 낮은 전압에서 높은 전압으로의 상승 또는 그 반대의 하강 시에만 업데이트된다는 것을 의미한다.

- edge-triggered clocking methodology에서는 state만이 데이터를 저장할 수 있으므로, 모든 Combi의 입력은 state에서 제공되어야 하고, 출력은 state에 기록되어야 한다. 입력은 이전 클럭 사이클에서 기록된 값이고, 출력은 다음 클럭 사이클에서 사용될 값이다.

- state가 매 클럭 엣지에서 기록된다면 쓰기 제어 신호(write control signal)를 표시하지 않지만, state가 매 클럭마다 업데이트되지 않는 경우에는 명시적인 쓰기 제어 신호가 필요하다. 이 때, 클럭 신호와 쓰기 제어 신호는 입력이며, 쓰기 제어 신호가 활성화되고 클럭 엣지가 발생할 때만 상태 요소가 변경된다.

- 신호가 논리적으로 높은 상태를 나타낼 때 “asserted” 되었다고 하며, 신호를 논리적으로 높게 설정하는 것을 “assert”라고 한다. 반대로 논리적으로 낮은 상태를 나타낼 때는 “deasserted”라고 한다. 하드웨어 구현 시에는 1이 논리적으로 높음을 나타낼 때도 있고, 낮음을 나타낼 때도 있어 이러한 용어를 사용하는 것이다.

엣지 트리거 방법론을 사용하면, 동일한 클럭 사이클에서 레지스터 내용을 읽고, 해당 값을 조합 논리를 통해 전송한 후, 다시 해당 레지스터에 기록할 수 있다.

Let’s build a datapath

각 MIPS instruction에 필요한 요소들을 하나하나씩 조립해 나가며, 전체 CPU를 구성하는 방법으로 설명할 것이다. 최상위 레벨에서 각 명령어가 필요한 데이터 경로 요소를 살펴보고, 그 다음으로 추상화 수준을 단계별로 낮추면서 설계를 구체화해 나간다. 데이터 경로 요소들을 설명할 때 제어 신호도 함께 설명한다.

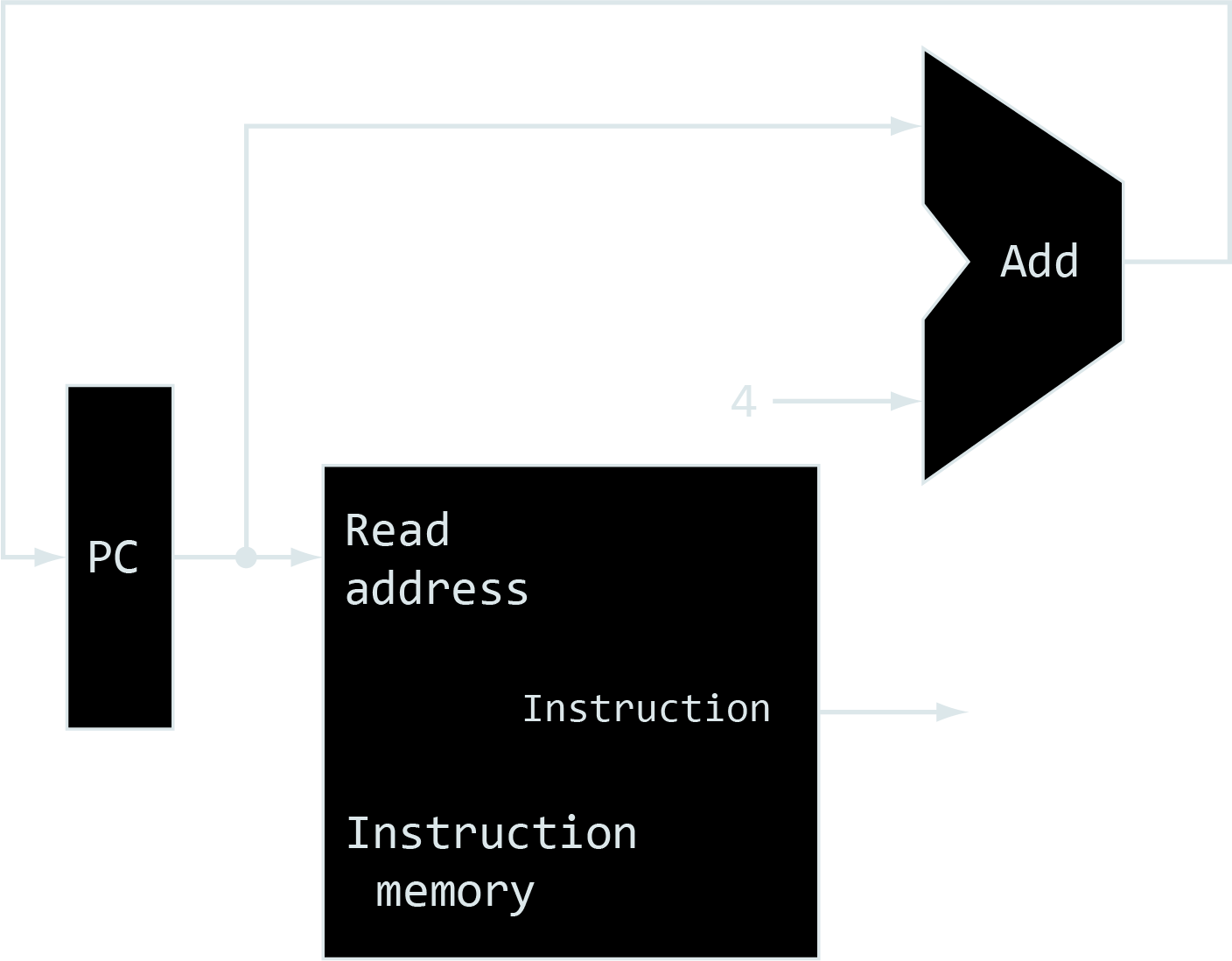

general

항상 기본적으로, 현대 컴퓨터는 내장형 프로그램 방식으로, 컴퓨터 연산에 필요한 명령어가 내부 메모리에 적재되어 있다. 항상 컴퓨터의 PC (program counter)는 다음 실행할 명령어를 가르키고 있고, 명령어를 실행한 뒤 PC를 다음 4 바이트로 옮겨야 할 것이다. (MIPS-32는 명령어의 크기가 32비트로 고정되어 있기 때문)

이를 순서로 나타내면,

- 명령어를 메모리에서 가져온다. (Fetch)

- PC가 이 명령어를 가르킨다.

- 명령어를 실행 후, 다음 명령어 주소를 가르킨다.

따라서, 다음 요소가 공통적으로 필요하다.

- Instruction memory

- Program counter

- Adder

Adder는 ALU의 특수한 경우로, 항상 덧셈 연산만을 수행한다. 여기까지의 구성 요소를 그려보면 다음과 같다.

R-format

R-format 명령어는, 2개의 레지스터를 읽은 뒤, 각 레지스터에 대해 ALU 연산을 수행한 뒤, 다시 결과값을 레지스터에 기록한다. add, sub, AND, OR, slt 등이 있다.

R-format의 경우, 세 개의 레지스터 피연산자가 필요하다. 두 개의 레지스터에서는 데이터를 읽고, 나머지 하나의 레지스터에 결과값을 써야 한다.

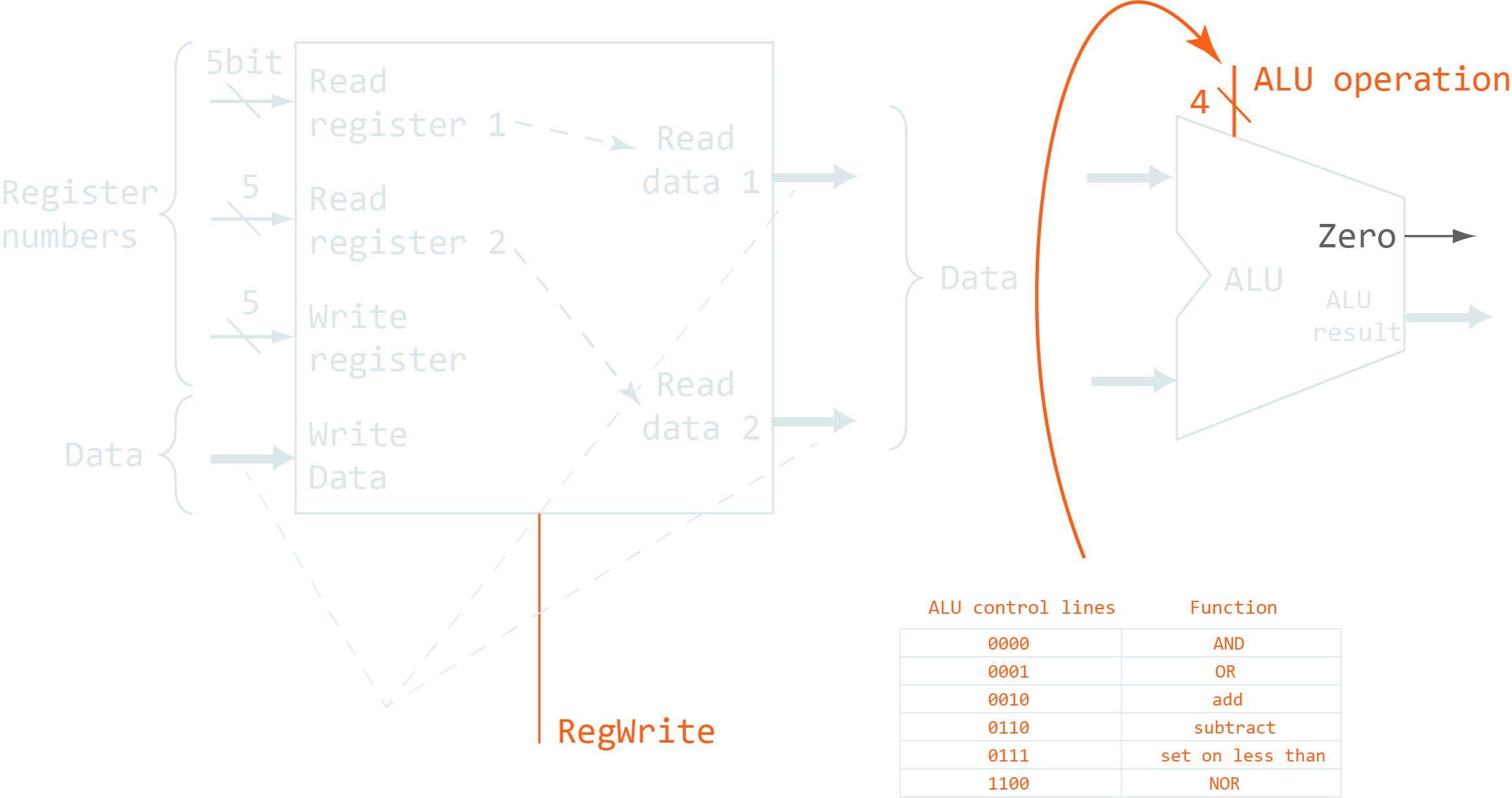

Register file

프로세서의 32개 범용 레지스터는 레지스터 파일(register file)이라는 구조에 저장된다. 레지스터 파일은 파일 내에서 특정 레지스터 번호를 지정하여 읽거나 쓸 수 있는 레지스터들의 모음이다. 레지스터 파일은 컴퓨터의 레지스터 상태를 저장하며, 또한 레지스터에서 읽은 값을 처리하기 위한 ALU가 필요하다.

따라서, 레지스터에서 읽을 각 데이터 워드에 대해

- 읽을 레지스터 번호를 지정하는 입력과

- 레지스터에서 읽은 값을 전달할 출력이 필요하다.

즉, 데이터를 쓰기 위해서는 기록할 레지스터 번호를 지정하는 입력과 레지스터에 기록할 데이터를 제공하는 입력이 필요하다. 레지스터 파일은 항상 Read 레지스터 입력에 해당하는 레지스터의 내용을 출력한다. 그러나 쓰기는 쓰기 제어 신호가 활성화된 경우에만 클럭 엣지에서 발생한다.

따라서, 총 네 개의 입력(세 개는 레지스터 번호 지정용, 하나는 데이터용)과 두 개의 출력(모두 데이터용)이 필요하다. 레지스터 번호 입력은 5비트 너비(32개의 레지스터를 지정하기 위해 ), 데이터 입력과 두 개의 데이터 출력 버스는 각각 32비트 너비이다.

ALU가 특정한 명령을 실행하기 위해 필요한 제어 신호도 필요하다. ALU의 4비트 제어 신호에 대한 자세한 설명은 나중에 이어서 하도록 하자.